# ВЛАДИМИРСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИМЕНИ АЛЕКСАНДРА ГРИГОРЬЕВИЧА И НИКОЛАЯ ГРИГОРЬЕВИЧА СТОЛЕТОВЫХ

На правах рукописи

#### TAXAAH OCAMA

# РАЗРАБОТКА КОРРЕКТИРУЮЩИХ КОДОВ ДЛЯ ИНФОРМАЦИОННОЙ ЗАЩИТЫ ТЕЛЕКОММУНИКАЦИЙ КОМПЬЮТЕРНЫХ СЕТЕЙ

Специальность:

05.12.13 - « Системы, сети и устройства телекоммуникаций »

Диссертация на соискание ученой степени кандидата технических наук

Научный руководитель: д.т.н., профессор Галкин А.П.

### СОДЕРЖАНИЕ

| СПИ  | СОК И                                                     | СПОЛЬЗУЕМЫХ СОКРАЩЕНИЙ                                    | 5  |  |  |  |  |  |

|------|-----------------------------------------------------------|-----------------------------------------------------------|----|--|--|--|--|--|

| BBE  | ДЕНИЕ                                                     | ······································                    | 7  |  |  |  |  |  |

| ГЛА  | BA 1.                                                     | ЗАЩИТА ТЕЛЕКОММУНИКАЦИОННЫХ                               |    |  |  |  |  |  |

| КОР  | ПОРАТ                                                     | ИВНЫХ КОМПЬЮТЕРНЫХ СЕТЕЙ                                  | 21 |  |  |  |  |  |

| 1.1. | <ol> <li>Основные понятия и допущения</li></ol>           |                                                           |    |  |  |  |  |  |

| 1.2. | Отказоустойчивые функциональные ядра телекоммуникационных |                                                           |    |  |  |  |  |  |

|      | систем                                                    |                                                           |    |  |  |  |  |  |

|      | 1.2.1.                                                    | Анализ отказоустойчивых ЭВМ                               | 25 |  |  |  |  |  |

|      | 1.2.2.                                                    | Анализ построения российских отказоустойчивых ЭВМ         | 30 |  |  |  |  |  |

|      | 1.2.3.                                                    | Построение отказоустойчивого ядра ТККС                    | 34 |  |  |  |  |  |

| 1.3. | Анализ                                                    | в резервирования на основе линейных кодов                 | 37 |  |  |  |  |  |

|      | 1.3.1.                                                    | Обоснование требований к методам кодирования              |    |  |  |  |  |  |

|      |                                                           | информации функционального ядра ТККС                      | 37 |  |  |  |  |  |

|      | 1.3.2.                                                    | Выбор метода кодирования, обеспечивающего минимальную     |    |  |  |  |  |  |

|      |                                                           | сложность декодирующего устройства                        | 40 |  |  |  |  |  |

|      | 1.3.3.                                                    | Исследование коррекции ошибок заданной кратности          | 42 |  |  |  |  |  |

|      | 1.3.4.                                                    | Проблема использования корректирующих кодов для           |    |  |  |  |  |  |

|      |                                                           | обеспечения отказоустойчивости функционального ядра       | 43 |  |  |  |  |  |

| 1.4. | Финан                                                     | совая и информационная безопасность и риски при           |    |  |  |  |  |  |

|      | проект                                                    | ировании                                                  | 45 |  |  |  |  |  |

| Выво | оды к гл                                                  | таве 1                                                    | 51 |  |  |  |  |  |

| ГЛА  | BA 2. C                                                   | БНАРУЖЕНИЕ И КОРРЕКЦИЯ ПРИ ФУНКЦИОНАЛЬНО-                 |    |  |  |  |  |  |

| КОД  | ОВОЙ                                                      | ЗАЩИТЕ ЯДРА ТККС                                          | 54 |  |  |  |  |  |

| 2.1. | Поэлем                                                    | иентная и комплексная информационная защита ТККС          | 54 |  |  |  |  |  |

| 2.2. | Разраб                                                    | отка модифицированных итеративных кодов повышенной        |    |  |  |  |  |  |

|      | обнару                                                    | живающей и корректирующей способности                     | 61 |  |  |  |  |  |

| 2.3. | Обосно                                                    | ования рациональной методики построения итеративного кода |    |  |  |  |  |  |

|      | для об                                                    | бнаружения и коррекции ошибок в устройствах хранения      |    |  |  |  |  |  |

|      | инфор    | мации функционального ядра ТККС                         | 03  |

|------|----------|---------------------------------------------------------|-----|

|      | 2.3.1.   | Оценка аппаратурных затрат на реализацию предлагаемого  |     |

|      |          | метода кодирования                                      | 65  |

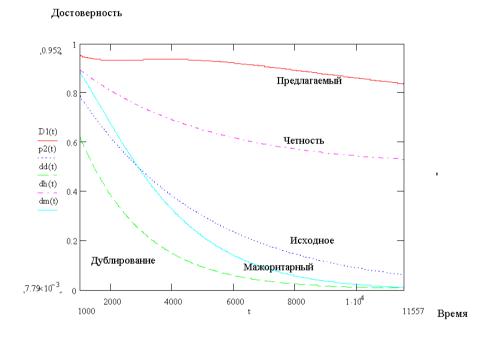

|      | 2.3.2.   | Достоверность функционирования отказоустойчивого        |     |

|      |          | запоминающего устройства                                | 71  |

|      | 2.3.3.   | Обоснование выбора метода обнаружения и коррекции       |     |

|      |          | ошибок в устройствах хранения и передачи информации     | 71  |

|      | 2.3.4.   | Сравнительная оценка аппаратурных затрат при реализации |     |

|      |          | предлагаемых методов кодирования информации             | 75  |

|      | 2.3.5.   | Сравнительная оценка достоверности функционирования при |     |

|      |          | реализации предлагаемых методов кодирования             |     |

|      |          | информации                                              | 77  |

|      | 2.3.6.   | Обоснование методик кодирования информации при          |     |

|      |          | увеличении числа информационных разрядов                | 77  |

|      | 2.3.7.   | Сравнительная оценка предлагаемого подхода с            |     |

|      |          | существующими методами                                  | 78  |

| 2.4. | Реком    | ендации для технической реализации предлагаемых методик |     |

|      | кодиро   | ования                                                  | 80  |

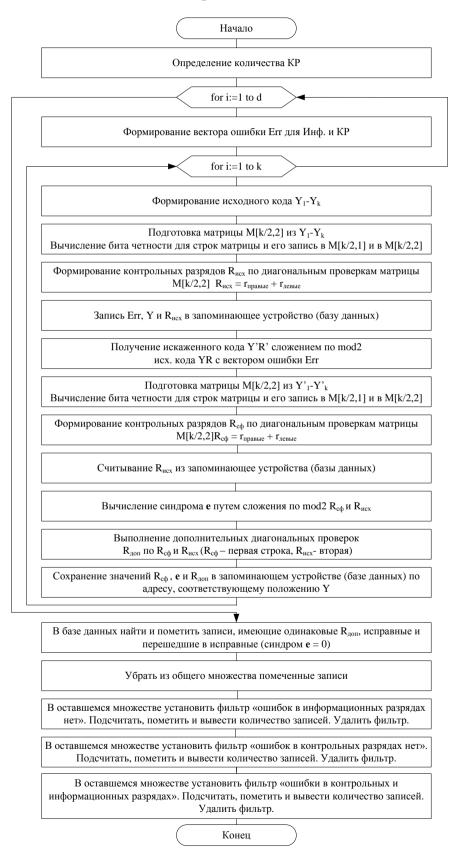

| 2.5. | Разраб   | отка методики алгоритмизации декодирования              | 81  |

| 2.6. | Модел    | ь функционально-кодовой защиты устройства памяти        | 84  |

| 2.7. | Анали    | з угроз информационной безопасности и основные          |     |

|      | мероп    | риятия по их предотвращению                             | 86  |

| Выв  | оды к г. | лаве 2                                                  | 90  |

| ГЛА  | BA 3.    | МЕТОДИКИ ЗАЩИТЫ ПРОЦЕССОРА И ЭЛЕМЕНТОВ                  |     |

| КИТ  | C        |                                                         | 91  |

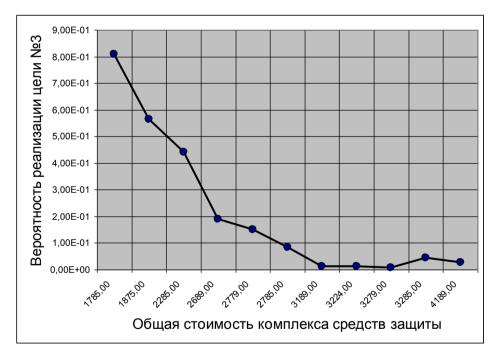

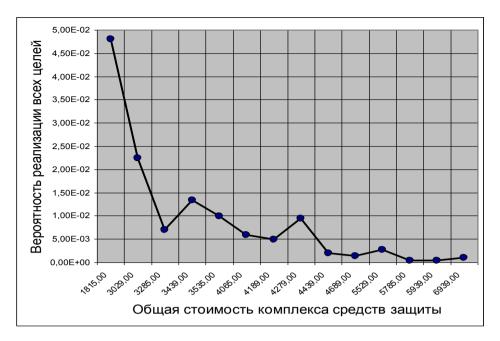

| 3.1. | Выбор    | комплекса защиты информации для корпоративных           |     |

|      | инфор    | мационно-телекоммуникационных сетей                     | 91  |

| 3.2. | Обесп    | ечение отказоустойчивости сумматора на основе           |     |

|      | коррен   | стирующих линейных кодов                                | 101 |

|      |          |                                                         |     |

| 3.3. | Разраб                                                 | ботка   | подх   | ода об                                  | бнаружения | И       | коррекц                                 | ии оп                                   | шибок                                   |     |

|------|--------------------------------------------------------|---------|--------|-----------------------------------------|------------|---------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----|

|      | арифм                                                  | етичес  | ких оп | ераций ф                                | ункциональ | ного яд | ра КСОН                                 | ł                                       |                                         | 103 |

| 3.4. | Разработка функционально-кодовой защиты процессора при |         |        |                                         |            |         | при                                     |                                         |                                         |     |

|      | выполнении логических операций                         |         |        |                                         |            |         |                                         | 106                                     |                                         |     |

|      | 3.4.1.                                                 | Разра   | ботка  | способа                                 | коррекции  | ошиб    | бок при                                 | выпол                                   | нении                                   |     |

|      |                                                        | опера   | ции сл | южения і                                | по mod 2   |         |                                         |                                         |                                         | 106 |

|      | 3.4.2.                                                 | Разра   | ботка  | способа                                 | коррекции  | ошиб    | бок при                                 | выпол                                   | нении                                   |     |

|      |                                                        | опера   | ции сд | цвига                                   |            |         |                                         | • • • • • • • • • • • • • • • • • • • • |                                         | 107 |

|      | 3.4.3                                                  | Разра   | ботка  | способа                                 | коррекции  | ошиб    | бок при                                 | выпол                                   | нении                                   |     |

|      |                                                        | логич   | еской  | операции                                | и ИЛИ      |         |                                         |                                         |                                         | 109 |

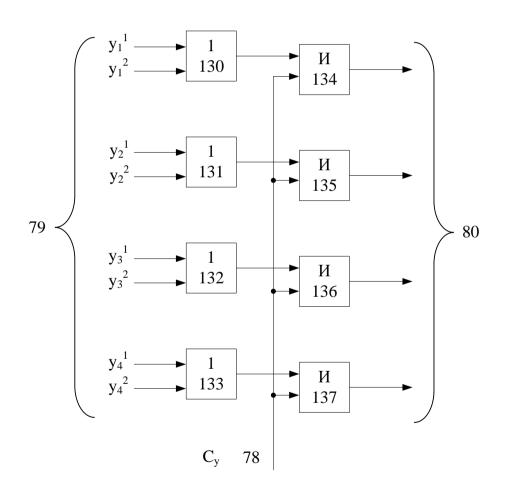

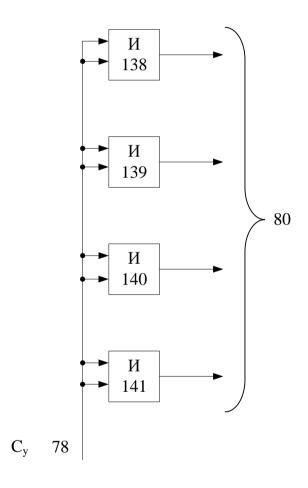

|      | 3.4.4                                                  | Разра   | ботка  | способа                                 | коррекции  | ошиб    | бок при                                 | выпол                                   | нении                                   |     |

|      |                                                        | логич   | еской  | операции                                | и И        |         |                                         |                                         |                                         | 110 |

|      | 3.4.5                                                  | Разра   | ботка  | методик                                 | и коррекци | и оши   | бок при                                 | выпол                                   | нении                                   |     |

|      |                                                        | логич   | еской  | операции                                | и НЕ       |         | • • • • • • • • • • • • • • • • • • • • |                                         |                                         | 112 |

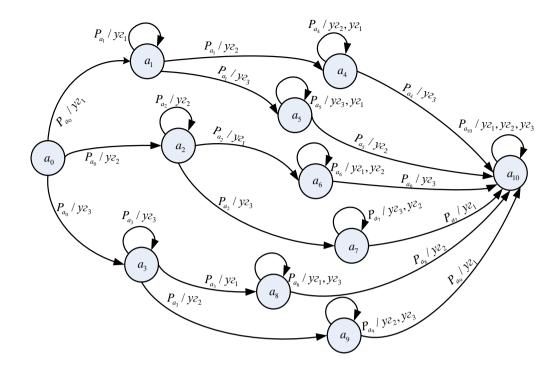

| 3.5. | Разраб                                                 | ботка ( | рункци | ионально:                               | й схемы от | казоуст | гойчивог                                | о проце                                 | eccopa                                  |     |

|      | повыш                                                  | іенной  | досто  | верности                                | функционир | ования  | I                                       |                                         |                                         | 113 |

| Выв  | оды к г.                                               | лаве 3. |        | • • • • • • • • • • • • • • • • • • • • |            |         | • • • • • • • • • • • • • • • • • • • • |                                         | • • • • • • • • • • • • • • • • • • • • | 142 |

| ЗАК  | ЛЮЧЕ                                                   | НИЕ     |        |                                         |            |         |                                         |                                         |                                         | 143 |

| СПИ  | ІСОК Л                                                 | ИТЕРА   | АТУРЬ  | J                                       |            |         |                                         |                                         |                                         | 145 |

| ПРИ  | ІЛОЖЕ                                                  | НИЕ 1   |        |                                         |            |         |                                         |                                         |                                         | 155 |

| ПРИ  | ІЛОЖЕ                                                  | ние 2   |        |                                         |            |         |                                         |                                         |                                         | 161 |

| ПРИ  | ІЛОЖЕ                                                  | ние 3   |        |                                         |            |         |                                         |                                         |                                         | 168 |

#### СПИСОК ИСПОЛЬЗУЕМЫХ СОКРАЩЕНИЙ

АБС - автоматизированная биллинговая система

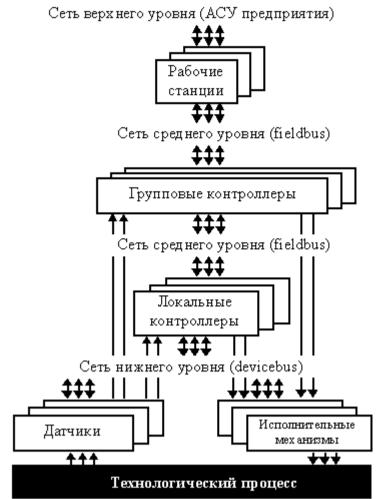

**АСУ ТП -** автоматическая система управления технологическими процессами

БВ - блок восстановления

БИС - большая интегральная схема

БУ - блок управления

**БЧХ -** коды Боуза-Чаудхури-Хоквингема

ГК - групповые контроллеры

ДК - дисковой контроллер

ЗИНВ - защита информации от непреднамеренного воздействия

ЗНСД - защита от несанкционированного доступа

3У - запоминающее устройство

ИБ - информационная безопасность

ИМС - интегральная микросхема

ИП - интерфейсный процессор

ИС - информационные системы

ИТ - информационные технологии

КИТС - корпоративная информационная телекоммуникационная сеть

КК - корректирующие коды

ККС - корпоративные КС

**КОГ**—**О**Д  $\Gamma$  - коды с коррекцией ошибок в одной группе и обнаружением в двух группах

КО—ОД - коды с коррекцией одиночной и обнаружением двойной ошибки

**КО—ОД—ООГ** - коды с дополнительной способностью обнаружения кратной ошибки в одной группе битов

КС - компьютерные сети

КСОН - КС особого назначения

**КТ—ОО -** код с коррекцией тройных и обнаружением одиночных ошибок **ЛК -** локальные контроллеры

НСД - несанкционированный доступ

ОЗУ - оперативное ЗУ

ПД - процессор данных

ПД - процессор данных

ПЗУ - постоянное ЗУ

ПК - персональный компьютер

ПЛИС - программируемая логическая интегральная схема

ПО - программное обеспечение

РабС - рабочие станции

РОш - регистр ошибок

РП - регистр повторения

РС - коды Рида-Соломона

СБИС - сверхбольшая интегральная схема

С3 - средства защиты

СС - схема сравнения

ТЗСК - триггер захвата от схем контроля

ТИД - триггер исходных данных

ТИОш - триггер игнорирования ошибок

ТККС - телекоммуникационные ККС

ТЭЗ - Типовой элемент замены

$\mathbf{y}\Gamma$  - угроз

УУП - устройство управления памятью

Ц - цель

ЦП - центральный процессор

ШИУ - шинное интерфейсное устройство

ЭВМ - электронная вычислительная машина

#### **ВВЕДЕНИЕ**

Аналогично мировой экономике современная экономика Сирии опирается на новейшие информационные и телекоммуникационные технологии.

В настоящее время в стране широко используются компьютерные сети, которые привели к бурному распространению глобальных информационных сетей, открывающих принципиально новые возможности информационного обмена.

В то же время, в информационном пространстве Сирии потенциально существует угроза использования различных приемов создания мешающих воздействий (кибертерроризма).

Кибернетический (кибертерроризм, терроризмом электронный терроризм) преследует основную направленную цель, на модификацию, блокирование несанкционированную или разрушение данных, нарушение заданных режимов функционирования информационнотехнических систем и их отдельных элементов, модификацию ИЛИ разрушение программ, внедрение вредоносных программ.

При этом преднамеренно или неумышленно создается опасность для жизни или здоровья людей или наступления других тяжких последствий, преследуются цели получения преимуществ при решении политических, экономических или социальных проблем. Кибертерроризм является одной из опасных преднамеренных угроз государственной и общественной безопасности и всей страны и отдельных корпоративных сетей.

Одним из перспективных направлений обеспечения работоспособности компьютерных сетей в экстремальных условиях, является разработка адаптивных отказоустойчивых систем, обеспечивающих автоматическое обнаружение, локализацию и исправление возникающих ошибок.

В свою очередь, в данной аппаратуре наиболее важное место занимает компьютер, предназначенный для управления и координации работы различных функциональных узлов, устройств, получения и обработки информации, систем контроля технического состояния системы и решения широкого круга других специфических задач поэтому, с точки зрения надежности и достоверности функционирования, особую актуальность приобретает вопрос обеспечения широкое использование в них автоматизированных систем управления.

**Объектом исследования** работы являются функциональные узлы компьютеров банковских электронных сетей, систем управления движением транспортных средств, правительственных систем связи, элементов технических систем безопасности Сирии.

Ответственность задач, возлагаемых на данную аппаратуру, определяет целый ряд специфических проблем, связанных с организацией обслуживания и обеспечением высокой эффективности рассматриваемой техники.

Данные системы, как правило, относятся к системам, восстанавливаемым вне процесса применения, важным показателем надёжности которых является вероятность безотказной работы.

Так как выдача ошибочной информации рассматриваемыми системами может привести к значительному ущербу, а в ряде случаев и к катастрофическим последствиям, то для систем такого рода в качестве основного показателя целесообразно использовать достоверность функционирования.

Под достоверностью функционирования устройства будем понимать свойство вычислительного устройства, характеризующее способность средств контроля признать результат работы устройства правильным или ошибочным при наличии пропуска ошибок или выдаче ложных сигналов ошибок средствами контроля.

Рассматриваемые системы относятся к объектам, работающим в реальном масштабе времени. Поток информации, поступающий в эти устройства, носит случайный характер, и устройство в любой момент времени должно быть готово к её обработке. Потеря текущей информации не может быть восполнена никакими иными способами. Переключение резерва в таких устройствах практически исключается.

Поэтому важной характеристикой рассматриваемых систем является их быстродействие.

Таким образом, при построении отказоустойчивых компьютерных сетей (КС) возникает необходимость обеспечения высоких значений вероятности безотказной работы, достоверности функционирования и быстродействия рассматриваемой аппаратуры.

Исходя из предъявляемых требований и условий применения КС, особую важность приобретает вопрос выбора средств обеспечения отказоустойчивости (средств обнаружения, локализации и коррекции возникающих ошибок).

#### Состояние исследуемого вопроса.

Структурные методы резервирования дискретных вычислительных устройств в Сирии специально не изучались, но они известны из мирового опыта и подробно рассмотрены в работах российских ученых С.М. Доманицкого, В.Е. Обухова, В.В. Сапожникова, Б.М. Каган и др.

В настоящее время для выявления ошибок КС широко используются коды, обнаруживающие ошибки.

Наиболее часто для обнаружения ошибок используется контроль по mod 2.

Недостатком используемого метода обнаружения ошибок (контроля по mod 2) является низкая обнаруживающая способность, так как при его использовании обнаруживается только 50% ошибок.

Для повышения процента обнаруживаемых ошибок данным методом информационные разряды разбиваются на отдельные блоки информации с организацией контроля по mod 2.

Следствием данного способа повышения процента обнаруживаемых ошибок является увеличение числа контрольных разрядов и аппаратурных затрат.

Организация контроля информации на основе кодов, обнаруживающих ошибки, позволяет повысить достоверность функционирования вычислителя, но не позволяет обеспечить отказоустойчивость дискретных устройств КС к постоянным отказам.

Для обеспечения отказоустойчивости могут использоваться три идентичные вычислительные машины, при возникновении отказа (обнаружения ошибки) в одном вычислителе его функции возлагаются на исправный вычислитель.

Недостатком данного подхода обеспечения отказоустойчивости является большая аппаратурная избыточность.

Наиболее **эффективным средством** достижения отказоустойчивости дискретных устройств являются **корректирующие коды,** позволяющие, в отличие от структурных методов резервирования, решать данную задачу при минимальных аппаратурных затратах резервного оборудования.

**Предметом исследования** является теория и методики обеспечения отказоустойчивости функциональных устройств КС на основе корректирующих кодов.

Вопросам использования корректирующих кодов для построения отказоустойчивых вычислительных систем посвящены российские работы А.М. Гаврилова, Н.Д. Путинцева, Ю.Л. Сагаловича, Е.С. Согомоняна, Я.А. Хетагурова, Н.С. Щербакова, А.А. Павлова и других ученых.

Среди зарубежных работ в области использования корректирующих кодов для решения вопросов обеспечения надёжности дискретных устройств

большое значение имеют труды фон Неймана, Мура и Шеннона, Ф.Дж. Мак-Вильямс, Э. Берлекэмп, У. Питерсон.

Анализ данных работ позволяет сделать вывод, что для обеспечения отказоустойчивости рассматриваемых вычислительных систем наиболее целесообразно использовать линейные коды.

Применение циклических кодов нежелательно, так как они реализуют последовательный метод декодирования, требующий больших временных затрат и, кроме этого, для исправления кратных ошибок требуется большое информационных разрядов, что исключает число возможность его обеспечения отказоустойчивости использования ДЛЯ мало разрядных вычислителей. Например, при исправлении ошибки в восьми разрядном модуле информации код Рида-Соломона требует 2040 информационных разрядов.

В настоящее время ДЛЯ обеспечения отказоустойчивости функциональных узлов КС наиболее широко используются корректирующие линейные коды, исправляющие одиночную ошибку, реализация которых требует минимальных аппаратурных затрат на кодирование и декодирование 30-40 % информации, составляющих относительно резервируемого устройства.

В этом случае предполагается, что в дискретных устройствах наиболее вероятно возникновение одиночных ошибок, так как в нормальных условиях эксплуатации радиоэлектронной аппаратуры до 75% составляют одиночные ошибки, а 25% составляют ошибки большей кратности.

На практике данное ограничение является не всегда оправданным, так как с увеличением сложности современных КС, а также в экстремальных условиях работы, (при воздействии электромагнитных или каких либо помеховых излучений и т.п.), возрастает вероятность неправильной коррекции из-за появления ошибок произвольной кратности, имеющих такой

же синдром ошибки, как и корректируемая (появления кратных ошибок, корректируемых как одиночная ошибка).

Поэтому, при построении отказоустойчивых вычислителей КС возникает необходимость использования корректирующих кодов, обнаруживающих и исправляющих кратные ошибки.

Однако в настоящее время мало эффективных методик построения линейных кодов исправляющих ошибки больше двукратной.

С другой стороны, использование линейных кодов исправляющих ошибки, позволяет обеспечить отказоустойчивость и высокую достоверность только устройств хранения информации, в то же время неизвестны эффективные использования методы корректирующих кодов ДЛЯ обеспечения отказоустойчивости преобразователей информации регистров сдвига, логических операций И, ИЛИ, HE. (сумматоров, суммирования по mod2), что является наиболее опасным, так как ошибка при расчетах начинает распространяться в вычислительном процессе.

Например, при контроле арифметических операций наиболее широко используется контроль по модулю (контроль по остаткам, т.е. остаток от результата суммы должен быть равен сумме остатков слагаемых), который требует больших временных и аппаратурных затрат и не позволяет исправлять возникающие ошибки, что является характерным и для других видов контроля (контроль по четности суммы, слагаемых, переносов; с использованием дублирования или пара фазной логики и т.д.).

Для контроля большинства логических операций невозможно сформировать контрольные разряды, которые оказались бы совместимыми с данными операциями, по этой причине наиболее широко используются метод повторения, который также требует временных затрат и обеспечивает требуемую отказоустойчивость И достоверность функционирования преобразователей информации.

Кроме этого, при использовании корректирующих линейных кодов для обеспечения отказоустойчивости вычислителей не учитываются функциональные особенности рассматриваемой аппаратуры (например, по приспособленности к техническому диагностированию).

Таким образом, проблемы использования корректирующих кодов заключается в следующем:

- для защиты памяти КС, работающих в реальном масштабе времени, могут быть использованы **только линейные коды**, при этом **не известны методы** построения линейных кодов, корректирующих больше двукратных ошибок;

- аппаратурные затраты на коррекцию одиночной ошибки составляют 30% относительно исходного ЗУ, двукратной -100%, при коррекции ошибки большей кратности  $C_{\text{ДЕК}} >> C_{\text{ИСХ}}$  (возникает проблема «сторожа над сторожем»);

- возникновение ошибок, кратность которых превышает корректирующие возможности кода, приводит к ошибочной коррекции;

- в настоящее время не известны методы построения корректирующих кодов, обеспечивающих коррекцию ошибок заданной кратности при условии обнаружения максимального количества некорректируемых ошибок.

Кроме этого, осуществление коррекции кратных ошибок на основе линейных кодов приводит к резкому увеличению избыточности кода и большим аппаратурным затратам на кодирование и декодирование информации, что не только не позволяет получить требуемый уровень достоверности функционирования отказоустойчивого устройства, но и приводит к снижению данного показателя, т.е. существует противоречие между необходимостью обнаружения и коррекции кратных ошибок специализированных КС и большими аппаратурными и временными затратами, связанными с обнаружением и исправлением кратных ошибок.

Концептуальным подходом, разрешающим данное противоречие, является разработка корректирующих линейных кодов, исправляющих ошибки заданной кратности при условии обнаружения максимального количества некорректируемых ошибок и требующих минимальных временных и аппаратурных затрат на их реализацию для обеспечения отказоустойчивости и высокой достоверности функционирования запоминающих устройств, с адаптацией данных методов кодирования для обеспечения отказоустойчивости и достоверности функционирования узлов (преобразователей информации) процессора.

**Цель диссертации:** разработка методического аппарата повышения отказоустойчивости функциональных узлов процессоров телекоммуникационных КС для обычных и экстремальных условий работы.

**Научная задача:** Разработка методического аппарата обеспечения отказоустойчивости процессора телекоммуникационных сетей на основе коррекции ошибок требуемой кратности при заданных временных и аппаратурных затратах на средства обнаружения и коррекции ошибок:

$$O(t) = O_{mpe\delta}(t) / C_K^O = C_{3AJJ}; \quad t_K^O = t_{3AJJ},$$

где O(t) - отказоустойчивость функционального узла КС;

$t_K^O, t_{3\!A\!J\!\!\!/}$  - временные затраты, соответственно, на коррекцию кратной ошибки и заданное время на обнаружение и коррекцию ошибки.

**Методы исследования.** При решении научной задачи использованы теоретические методы исследований, основанные на научных положениях: теории линейных корректирующих кодов, теории множеств, теории дискретных автоматов, теории надежности и элементов нечеткой логики.

#### Положения выносимые на защиту:

- 1. Модифицированный итеративный код повышенной корректирующей способности.

- 2. Методический аппарат функционально-кодовой защиты процессора при выполнении арифметических и логических операций.

- 3. Методика построения структур защищенных вычислителей КС.

#### Новизна научных исследований заключается в:

- 1. Предложен модифицированный итеративный линейный код повышенной обнаруживающей и корректирующей способности, адаптированный для защиты преобразователей информации КС.

- 2. Предложен методический аппарат функционально-кодовой защиты процессора при выполнении арифметических и логических операций.

- 3. Разработана методика построения структур защищенных вычислителей КС.

#### Практическая значимость результатов работы состоит в следующем:

- решение рассматриваемой задачи имеет важное значение для Сирии, ожидаемые научные результаты позволяют создать качественно новый уровень отказоустойчивости КС и обычных и в экстремальных условиях работы;

- в зависимости от правила проведения дополнительных проверок, предлагаемые методики позволяют корректировать от 50% до 94% обнаруживаемых ошибок, обеспечить отказоустойчивость и достоверность функционирования компьютерных сетей в реальном масштабе времени, практически без снижения быстродействия исходного устройства.

Достоверность полученных результатов подтверждается использованием математической модели, адекватно отображающей реальные процессы, протекающие в дискретных устройствах, обоснованием и доказательством впервые полученных научных результатов и выводов,

применением широко известных частных научных результатов, результатами внедрения разработок, ясной физической интерпретацией полученных результатов и их непротиворечивостью с существующими методами коррекции ошибок отказоустойчивых вычислителей.

#### Апробация работы.

Основные положения диссертационной работы докладывались и обсуждались на 4-х международных конференциях: 8-й Международной НТК «Перспективные технологии в средствах передачи информации», Владимир, РФ, 2009г.; Международной НК «Экономическая проблемы ресурсного обеспечения инновационного развития региона» Владимир, РФ, 2009г.; Международной НПК «Факторы развития региональных рынков» Владимир, РФ, 20011г.; 9-й Международной НТК «Перспективные технологии в средствах передачи информации», Владимир, РФ, 2011г.

Публикации. Результаты работы отражены в 11-ти научных трудах, в том числе в 3-х статьях Всероссийского издания из перечня ВАК («Известия института инженерной физики»); в 2-х отчетах о НИР ( ГБ №118, ВлГУ).

#### Результаты научных исследований реализованы:

при разработке отказоустойчивого вычислителя для КС ( акты внедрения см. приложения );

Диссертационная работа состоит из введения, трех глав и приложений.

**Во введении** проводится обоснование актуальности и научной значимости поставленной научной задачи, исследование состояния вопроса и постановка цели научных исследований, применительно, в частности, к Сирии.

**В первой главе** проводится анализ методик построения отказоустойчивых автоматизированных систем контроля, выбрана модель исследований, введены основные понятия, приняты ограничения и допущения, выявление существующих противоречий.

Обоснована целесообразность и выявлены особенности использования корректирующих кодов для обеспечения отказоустойчивости систем памяти KC. Определен класс корректирующих линейных кодов, требующих затрат минимальных аппаратурных на кодирование и декодирование информации.

Определена проблема использования корректирующих кодов для обеспечения отказоустойчивости преобразователей информации вычислителей КС.

**Вторая глава** посвящена разработке модифицированного итеративного кода повышенной обнаруживающей и корректирующей способности.

В результате проведенных исследований в работе были предложены шесть подходов построения модифицированных итеративных кодов.

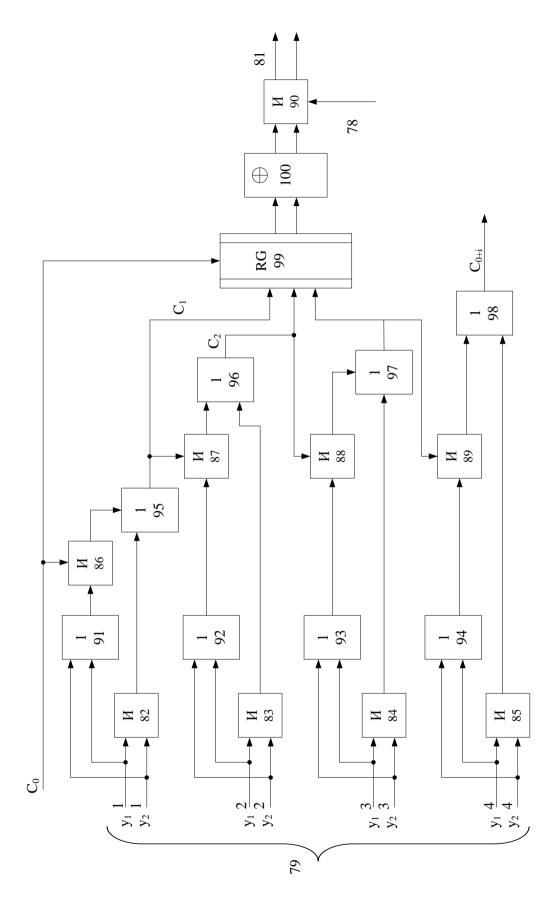

Предлагаемые методы кодирования включают следующие основные положения: информация представляется в две строки, в каждой строке проводится проверка на четность, организуются диагональные проверки с участием, либо без участия контрольных разрядов.

Существенным отличием построения предлагаемых модифицированных итеративных кодов от известных является организация дополнительных диагональных проверок при вычислении синдрома ошибки, относительно двух строчной матрицы построенной на основе переданных значений контрольных разрядов и значений контрольных разрядов, сформулированных основе значений полученных на информационных разрядов, что позволило повысить В два раза корректирующие возможности итеративного кода.

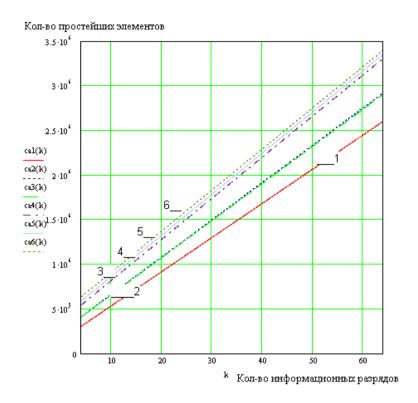

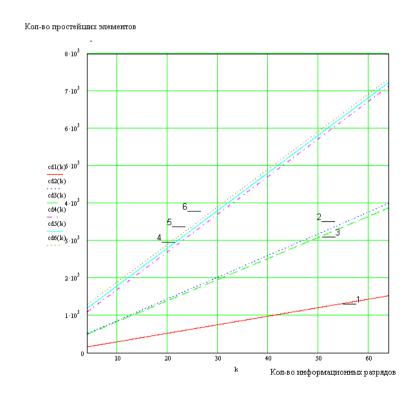

Проведены исследования по расчету аппаратурных затрат на реализацию кодирующего и декодирующего устройства при использовании предлагаемых подходов, обоснована кратность исправляемой ошибки.

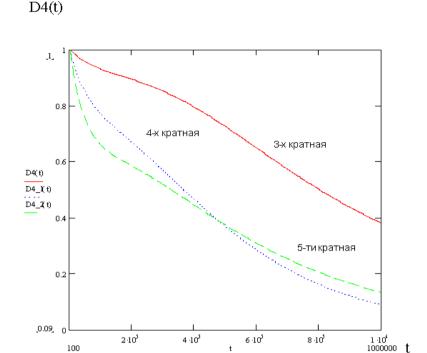

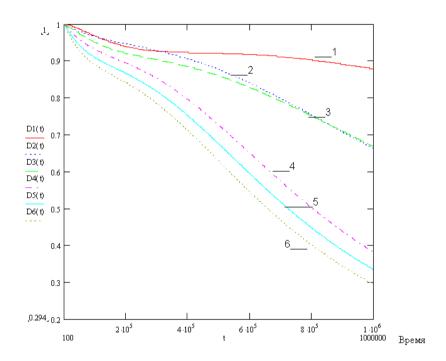

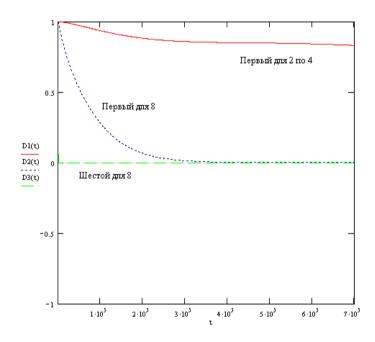

Установлено, что наименьшие аппаратурные затраты соответствуют модифицированному итеративному коду, исправляющему трехкратные ошибки в полубайте информации при этом, наибольшей обнаруживающей и корректирующей способностью обладает шестой подход (корректирует 94 % от общего количества возможных ошибок) однако, наименьшее количество контрольных разрядов, наименьшие аппаратурные затраты соответствуют модифицированному итеративному коду при использовании первого подхода кодирования, который был принят для обеспечения отказоустойчивости устройств хранения и передачи информации.

Защищать информационную систему имеет смысл только комплексно.

## Предлагаемые методики модифицированных итеративных кодов позволяют:

- 1. корректировать трехкратные полубайте ошибки ошибки информации (в настоящее время неизвестны эффективные методы построения линейных кодов исправляющих больше двух - кратной ошибки), при условии обнаружения ошибок в остальных разрядах кодового набора, за исключением ошибок трансформируемых в разрешенные кодовые наборы (новое свойство линейного кода - коррекция ошибок заданной кратности при обнаружения максимального количества некорректируемых условии ошибок), при этом обеспечивается возможность:

- 2. исправлять ошибки различной конфигурации (имеет свойства нелинейного кода) при условии обнаружения некорректируемых ошибок;

- 3. осуществлять коррекцию модульных ошибок при малом числе информационных разрядов, т.е. исключить основной недостаток кода Рида-Соломона (при исправлении ошибки в восьми разрядном модуле информации код Рида-Соломона требует 2040 информационных разрядов поэтому исключается возможность его использования для обеспечения отказоустойчивости мало разрядных специализированных вычислителей КС);

- 4. иметь минимальные временные затраты на декодирование (в отличие от кодов Рида-Соломона реализующих процедуру циклического декодирования);

- 5. исключить влияние неисправного резервного оборудования на работу устройств КС при наличии ошибок в контрольных разрядах и отсутствии ошибок;

- 6. сигнализировать о неисправности устройства памяти при возникновении некорректируемой ошибки.

**Третья глава** посвящена разработке функционально-кодовой защиты процессора при выполнении арифметических и логических операций (адаптации предлагаемого модифицированного кода для защиты данных операций).

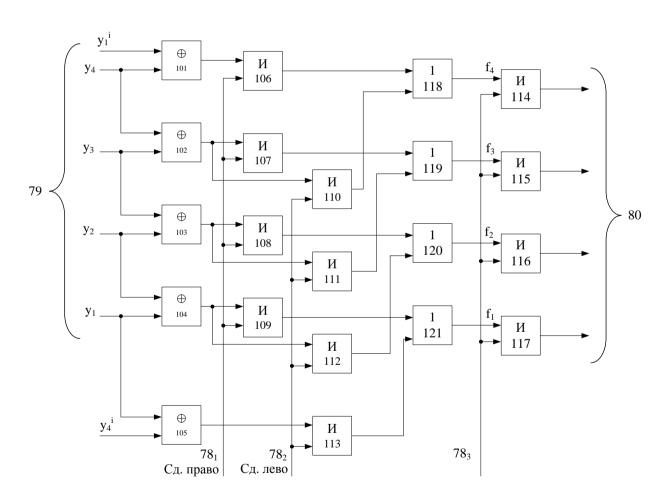

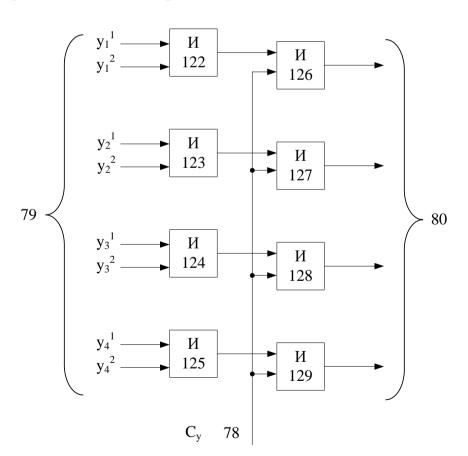

Для формирования "правильных" значений контрольных разрядов возникает необходимость определения правил формирования поправки к значению контрольных разрядов, полученных в результате выполнения арифметической операции  $S_{k+}$ .

Правило формирования поправки, при выполнении операции сложения основано построения матрицы поправок, учитывающих перенос единицы в старший разряд, при наличии единиц в одноименных разрядах.

**Выявлены свойства** корректирующих кодов, позволяющие сформулировать правила формирования контрольных разрядов для логических операций.

#### Основные результаты научных исследований

В результате проведенных исследований разработан научнометодический аппарат функционально-кодовой защиты КС, позволяющий решить задачу обеспечения отказоустойчивости функционирования рассматриваемых систем в экстремальных условиях работы при выполнении ограничений на временные и аппаратурные затраты. При решении рассматриваемой научной проблемы получены следующие основные результаты:

- 1. Сформулирована концепция обеспечения отказоустойчивости вычислителей КС для экстремальных условий работы.

- 2. Разработаны правила построения модифицированного итеративного линейного кода повышенной обнаруживающей и корректирующей способности, отличающегося от известных методов организацией дополнительных проверок при формировании синдрома ошибки, позволяющих существенно повысить корректирующие способности итеративного кода. Предлагаемая методика применения модифицированных кодов, в отличие от существующих методов, позволяет:

осуществлять построение отказоустойчивых ЗУ при малом числе информационных разрядов;

корректировать трехкратные ошибки в полубайте информации при условии обнаружения некорректируемых ошибок;

исправлять ошибки заданной конфигурации.

- 3. Выявлены свойства, и разработаны теоретические положения, позволяющие создать методический аппарат функционально-кодовой защиты процессора при выполнении арифметических и логических операций (впервые разработана процедура адаптации линейных кодов для защиты преобразователей информации).

- 4. Разработана **функциональная модель,** отказоустойчивого процессора, реализующего предлагаемый методический аппарат.

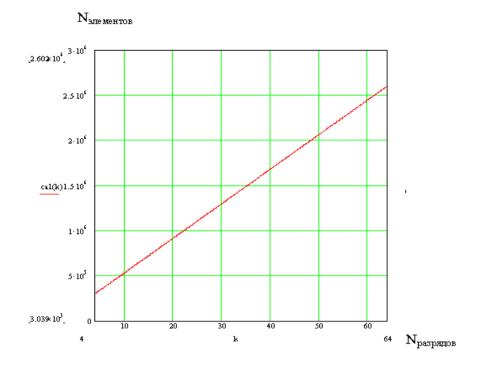

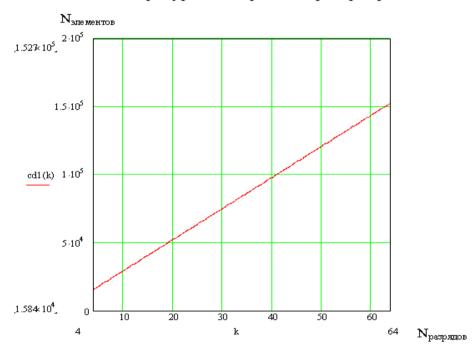

- 5. Получено выражение для оценки аппаратурных затрат, вводимых для обеспечения отказоустойчивости при использовании предлагаемой методики кодирования информации, и проведен анализ избыточности в зависимости от разрядности корректируемой модульной ошибки, проведена оценка выигрыша в достоверности функционирования отказоустойчивого устройства, по сравнению с существующими методами.

Полученные научные результаты свидетельствуют о решении крупной научной проблемы, связанной с достижением качественно нового уровня обеспечения отказоустойчивости КС, необходимого для поддержания их живучести в экстремальных условиях работы.

Решение рассматриваемой научной задачи имеет важное значение для Сирии, которое за пределы обеспечения достоверности выходит функционирования компьютерных телекоммуникационных сетей. Разработанный методический аппарат позволяет обеспечить комплексное решение научной задачи повышения вероятности безотказной работы и достоверности функционирования телекоммуникационных устройств, работающих в реальном масштабе времени.

### ГЛАВА 1. ЗАЩИТА ТЕЛЕКОММУНИКАЦИОННЫХ КОРПОРАТИВНЫХ КОМПЬЮТЕРНЫХ СЕТЕЙ

#### 1.1. Основные понятия и допущения

Высокая эксплуатационная надежность КС требует включения в своем составе функциональное ядро (специализированную ЭВМ) имеющую, в свою очередь, средства (аппаратурные, микропрограммные, программные), позволяющие автоматически восстанавливать процесс выполнения программы после значительной части возможных ошибок в ее работе.

Сохранение работоспособности функционального ядра при отказах имеет особенно большое значение при эксплуатации систем, работающих в реальном масштабе времени.

Автоматическое восстановление вычислительного процесса при отказах может быть достигнуто путем введения в ЭВМ свойств отказоустойчивости [18].

Отказоустойчивыми будем называть системы, обеспечивающие автоматическое обнаружение ошибки, выявление ее характера (случайная или постоянная), изоляцию неисправности, реконфигурацию системы и восстановление вычислительного процесса [27].

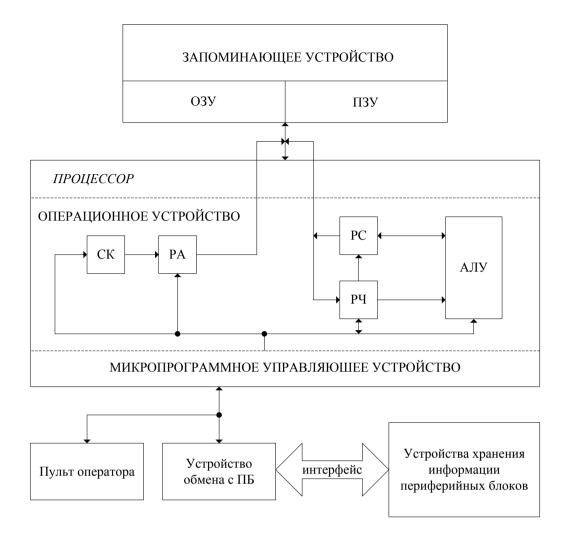

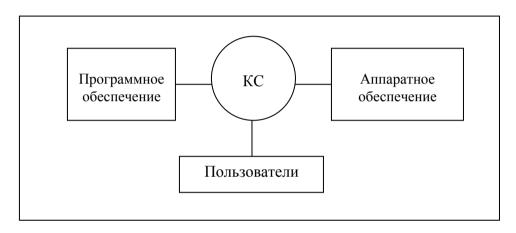

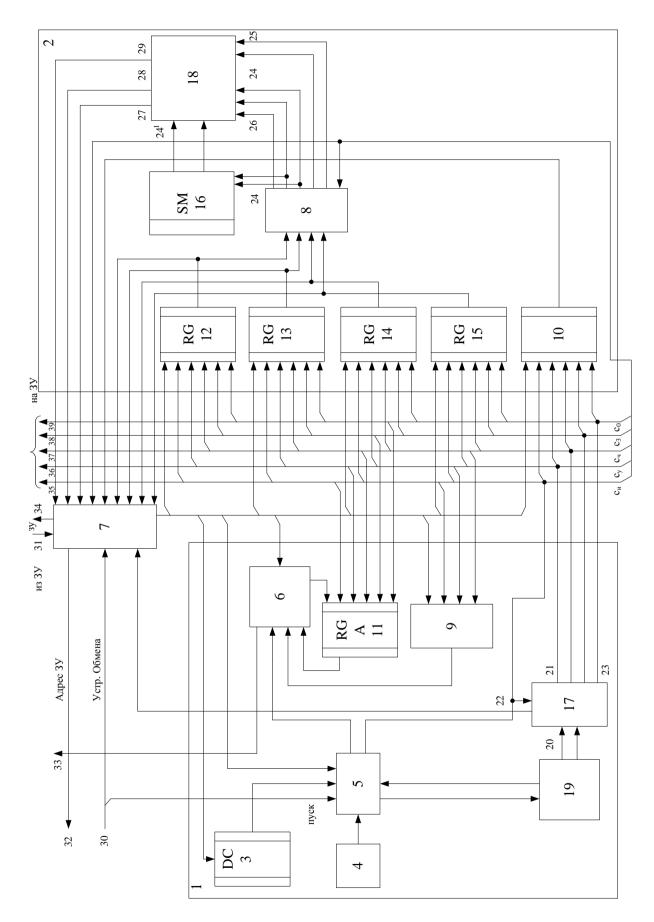

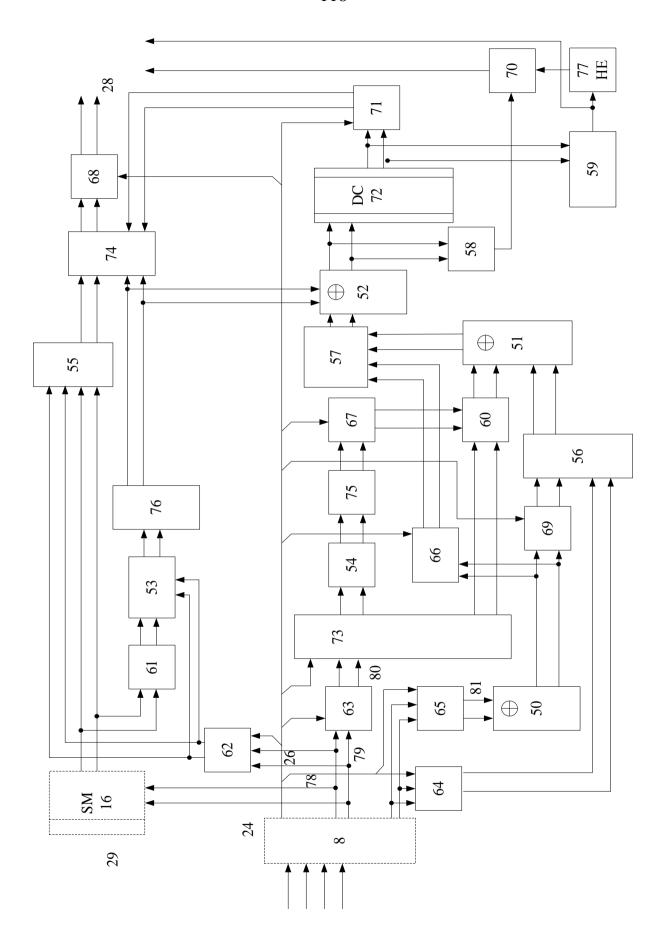

В упрощенном виде вычислитель телекоммуникационных компьютерных сетей может быть представлена одноадресной ЭВМ, как правило, с микропрограммным управляющим устройством, работающей с числами с фиксированной запятой в не модифицированном дополнительном коде (рис. 1.1.1).

Рис. 1.1.1. Упрощенная структурная схема вычислителя

Основу вычислителя составляет процессор, состоящий из двух основных устройств - операционного и управляющего. Операционное устройство включает в свой состав: арифметико-логическое устройство (АЛУ, использующее k-разрядный комбинационный сумматор параллельного типа);

СК- счетчик команд;

РА-регистр адреса;

РС- регистр сумматора (аккумулятора);

РЧ – регистр числа.

Устройство управления микропрограммного типа, конструктивно выполнено в виде постоянного запоминающего устройства.

Запоминающее устройство состоит из постоянного (ПЗУ) и оперативного (ОЗУ) полупроводниковых запоминающих устройств.

Обмен информацией между вычислителем и периферийными устройствами осуществляется по цифровому интерфейсу с помощью устройства обмена [13,14].

Для ТККС в состав вычислителя входит пульт оператора, предназначенный для ввода информации оператором, вывода информации и признаков состояния системы на панель индикации.

Допущения, принятые при исследовании функциональной модели дискретных устройств:

сигналы, поступающие на вход дискретного устройства идеальны;

дискретное устройство состоит из блоков одинаковой сложности (т.е. блоки содержат равное количество логических элементов), и их вероятности безотказной работы равны;

блоки построены из однотипных логических элементов (элементы, выполняющие вспомогательные функции, такие, как формирователи и т.п. при рассмотрении не учитываются).

Под отказом будем понимать событие, заключающееся в нарушении работоспособного состояния соответствующего дискретного устройства [41].

Несоответствие выходной информации функционального узла вычислителя относительно рассматриваемых входных воздействий (вызванное отказом) будем считать ошибкой [42].

Ограничимся рассмотрением ошибок дискретных устройств, которые проявляются в виде постоянных значений логических сигналов на его выходах типа  $const\,0$  и  $const\,1$ .

Если ошибка проявляется на одном выходе устройства, то ее будем называть одиночной ошибкой, на двух и более выходах устройства – кратной ошибкой.

Допустим, что рассматриваемые ошибки носят групповой (алгебраический) характер, могут быть одиночными, кратными и являются симметричными.

Предположим, что возникающие неисправности являются правильными, т.е. дискретное устройство, имеющее некоторую неисправность, описывается моделью, принятой для описания исправного устройства.

К возникновению ошибок в полупроводниковых интегральных микросхемах приводят различные физико-химические факторы [63].

Так, например, при эксплуатации БИС ЗУ основной причиной сбоев является наличие в материале полупроводника молекул урана и тория, распад которых вызывает появление альфа-частиц, причём, чем выше плотность упаковки элементов в кристалле, тем сильнее влияние этого фактора, а также, солнечная радиация.

Второй причиной отказа являются космические лучи. Если на уровне моря доля сбоев, вызванных космическими лучами, составляет 10%, то на высотах 10 - 15км интенсивность космических лучей возрастает в 150 раз. Так при исследовании воздействия альфа частиц на модуль памяти фирмы HARRIS HM 6508 ёмкостью 16 килобайт за 371 день полёта спутника наблюдалось 72 сбоя [98].

Кроме этого, в процессе эксплуатации на аппаратуру действует ряд независимых один от другого факторов. Прежде всего, происходит старение элементов схемы. На работу системы также влияют флюктуации, связанные с изменением температуры, величин нагрузки, электромагнитные наводки, изменение значений питающих напряжений и другие внешние факторы.

Многочисленные исследования и опыт эксплуатации дискретных устройств в нормальных условиях позволяют определить параметры возникающих ошибок [42]:

однократные ошибки......75...80%;

В экстремальных условиях работы ТККС (в условиях воздействия факторов), вредных учитывая, ЧТО вредные факторы воздействуют ошибок одновременно все системы, возникновение на элементы произвольной кратности следует считать равновероятным событием. Особую актуальность приобретает решение задачи по обеспечению достоверности функционирования и отказоустойчивости ТККС в экстремальных условиях работы.

## 1.2. Отказоустойчивые функциональные ядра телекоммуникационных систем

#### 1.2.1. Анализ отказоустойчивых ЭВМ

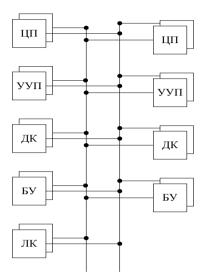

Отказоустойчивая ЭВМ фирмы Stratus содержащую следующие устройства [4] (рис.1.2.1): центральный процессор (ЦП), устройство управления памятью (УУП), дисковый контроллер (ДК), блок управления (БУ), ленточный контроллер (ЛК) и общую шину.

Каждое устройство системы задублировано и каждое дублированное устройство, в свою очередь, проверяется в процессе функционирования с помощью такого же устройства. Фактически в каждое функциональное устройство (ЦП, УУП, ДК, БУ) реализовано в виде двух самостоятельно проверяемых блоков, в которых для построения средств встроенного контроля используется дублирование.

В случае неисправности какого-либо блока системы производится переключение на исправную пару устройств. Факт неправильной работы фиксируется несовпадением выходных результатов устройств, образующих самопроверяемый блок. Поскольку общая шина также задублирована, то при отказе одной производится переключение на исправную шину.

Таким образом полная отказоустойчивость в системе Stratus достигается за счет значительных аппаратурных затрат, но при этом гарантируется высокая полнота обнаружения неисправностей (за счет контроля дублированием).

Рис. 1.2.1. Отказоустойчивая ЭВМ фирмы Stratus

Интересной особенностью рассматриваемой системы является исключение временных затрат для восстановления по сбоям. При анализе выходных результатов какой-либо пары устройств эта пара исключается из рабочей конфигурации и подключается исправная пара. Затем с помощью определяется вид неисправности (устойчивая неустойчивая) и в случае устойчивой неисправности производится замена неисправного устройства пары. После этого самопроверяемый блок вводится в систему. Поскольку в системе восстановление выполняется на уровне аппаратуры, то никакие программные способы образования контрольных используются. Кроме того, в системе не предусмотрена возможность рассылки между блоками информации об их состоянии. Как следствие, все это существенно упростило систему.

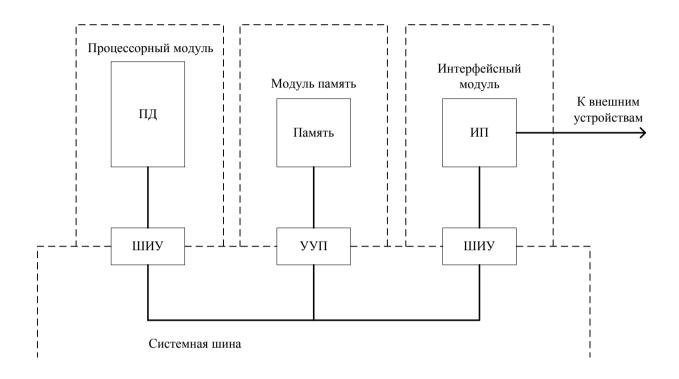

Отказоустойчивая вычислительная система фирмы Intel. Система Intel, была задумана и спроектирована как некоторая универсальная система, обладающая двумя основными свойствами: расширяемостью и

отказоустойчивостью, реализованными аппаратурной [7]. В системе на аппаратурном уровне выполняется восстановление по отношению к постоянным отказами и к кратковременным сбоям, причем не только процессоров, но и блоков памяти и интерфейсных шин.

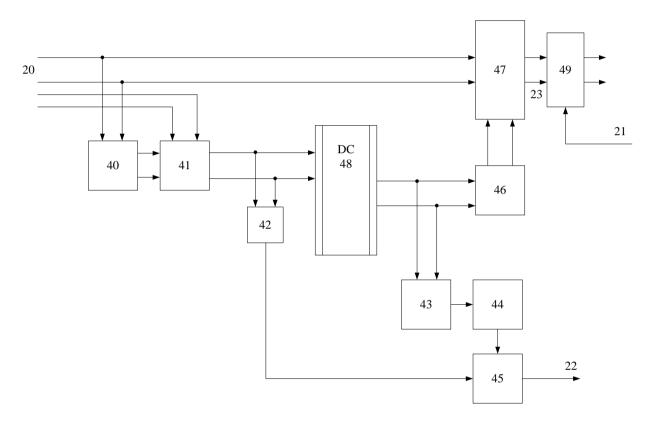

Основная базовая конфигурация системы содержит три 32-разрядных модуля (рис.1.2.2); процессорный модуль, модуль памяти, интерфейсный модуль, а также системную шину. Система построена на пяти СБИС: процессор данных (ПД), который состоит из двух СБИС; интерфейсный процессор (ИП); устройство управления памятью (УУП); шинное интерфейсное устройство (ШИУ).

Система является проблемно-ориентированной с архитектурой, ориентированной на язык программирования АДА [4].

Шинное интерфейсное устройство и УУП позволяют расширить систему; УУП обеспечивает работу с динамической оперативной памятью.

Разделение ресурсов, межпроцессорное взаимодействие в системе, доступ к памяти выполнены посредством введения специальных сигнальных шин, что обеспечивает модульную наращиваемость системы и дает возможность восстанавливать систему, не прерывая процесса ее функционирования.

Поскольку в системе все сигналы формируются независимо от ресурсов системы, наличие или отсутствие кого-либо модуля не влияет на процесс взаимодействия между остальными модулями. В системе отсутствует централизованное устройство арбитража шин, что позволяет всем ШИУ и УУП выполнять свой собственный доступ к системной шине.

Системная шина представляет собой многократно повторяемые 1разрядные адресные шины и 16-разрядные шины данных, поддерживающие 24-разрядное адресное пространство оперативной памяти. Любая одна передача по системной шине может содержать 1 ... 16 байт данных. С целью оптимизации пропускной способности системной шины каждая передача делится на отдельные пакеты запросов и ответов. Запросы и ответы могут проходить по (системной шине в то время, как УУП обрабатывает запрос.

Рис. 1.2.2. Базовая конфигурация системы Intel

Представленная система обладает свойствами отказоустойчивости. Системная шина защищена кодом с проверкой на нечетность, причем для шин данных и управления вводятся свои независимые разряды четности. Таким образом, на системной шине контролируются все одиночные неисправности и многие кратные.

Каждый модуль памяти защищен корректирующим кодом, обеспечивающим коррекцию одиночных ошибок и обнаружение двойных. Адресные ошибки также контролируются, поскольку контрольные разряды при записи в память формируются на основании как данных, которые будут записаны в память, так и адреса, по которому должны быть данные записаны.

УУП обеспечивает возможность программным способом использовать имеющийся в памяти один резервный разряд. Вся оперативная память содержит 40 кристаллов: 32 разряда данных, 7 контрольных разрядов корректирующего кода и 1 резервный разряд. Резервный разряд может подключаться взамен одного неисправного из 39 разрядов.

Для обеспечения отказоустойчивости в системе применяются самопроверяемые модули. Важным понятием в отказоустойчивой системе является понятие зоны распространения ошибки. Зона определяется как модуль или системная шина, которые ограничены контролируемыми интерфейсами.

Средства обнаружения ошибок располагаются в каждом контролируемом интерфейсе. Такое разбиение системы на зоны позволило существенно упростить алгоритм обнаружения и изоляции ошибок. На рис. 1.2.2 штриховыми линиями выделены 4 зоны распространения ошибок.

Зона распространения ошибок ПД включает в себя ПД, его ШИУ, процессорную шину и вспомогательную логику. Ошибки ПД контролируются путем дублирования СБИС (кристаллов), из которых состоит ПД, и сравнения результатов их работы.

Схема самопроверяемого модуля, состоящего из двух ПД, каждый из которых может быть как основным, так и контролирующим. Выбор статуса ПД (основной или контролирующий) производится при инициализации системы. Оба ПД работают синхронно, параллельно и с одинаковыми данными. Результаты их работы сравниваются схемой сравнения (СС). Например, основным по статусу может являться верхний ПД и результаты работы двух ПД сравниваются на схеме сравнения. При этом сигнал запрета поступает на нижнюю схему с тремя состояниями.

В результате выходная информация основного ПД будет поступать как на выход пары, так и на вход схемы сравнения, на второй вход которой поступает выходная информация контрольного ПД. При неисправности,

возникшей в основном или контрольном ПД, на выходе схемы сравнения появится сигнал ошибки. Если поменять статусы ПД (основной, контрольный), то сравнение будет выполнять вторая СС и сигнал запрета будет поступать на верхнюю схему с тремя состояниями.

Интерфейсный модуль, УУП, ШИУ также выполнены в виде самопроверяемых модулей, контроль в которых осуществляется дублированием со сравнением.

После того, как в системе будет обнаружена ошибка, выполняется восстановление путем повторения. В течение того временного цикла, когда была зафиксирована ошибка, обмены все ПО системной шине приостанавливаются и отменяются все запросы на обмен по системной шине. Система входит в состояние ожидания, что позволяет устранить влияние кратковременных сбоев. Состояние ожидания может длиться от 16 мкс до 2 с. Время ожидания устанавливается программным способом. По истечении времени ожидания все текущие запросы на обмен (и те, которые были отменены) повторяются ШИУ, что позволяет выполнять восстановление по отношению к сбоям и к одиночным корректируемым отказам в памяти [102,103].

Свойство наращиваемости позволяет организовать систему с непрерывным функционированием при наличии отказов в модулях. Уровень вводимой в систему избыточности устанавливается программно. Восстановление вычислительного процесса выполняют УУП и ШИУ без какой либо программной поддержки.

Система позволяет объединять самопроверяемые модули в пары. При этом один модуль пары является основным, а второй — «теневым». Фактически при такой организации системы все устройства учетверяются по сравнению с неизбыточной конфигурацией.

#### 1.2.2. Анализ построения российских отказоустойчивых ЭВМ

Большое внимание вопросам отказоустойчивости уделялось при производстве вычислительных систем на базе EC-ЭВМ [4].

Так, в процессоре этих машин предусматривалось аппаратурномикропрограммное повторение относительно сбоя. В этом случае, при принятом совмещении инструкций по нескольким уровням предусмотрена организация повторения инструкции или ее части. В аппаратуру повторения входят дополнительные регистры для сохранения информации, которая может быть изменена при выполнении операций процессора.

регистрах сохраняется дополнительных состояние начальной выборки инструкции, код операции, адрес инструкции, содержимое регистра состояний И Дополнительные регистры устанавливаются T. Д. микропрограммной время выполнения инструкции). Среди (BO предусмотрен регистр повторения, который указывает тип выполняемой операции и этап ее выполнения и обеспечивает повторение с требуемого места.

Взаимодействие между аппаратурой и микропрограммой повторения по сбою осуществляется блоком восстановления, состоящим из регистра ошибок (РОш) и комбинационной части. При обнаружении ошибки схемами контроля производится блокировка синхронизации процессора, т. е. прекращение выполнения инструкции, сигнал ошибки запоминается в РОш. По сигналу от блока восстановления (БВ) производятся запись ситуации и запуск микропрограммы повторения. Восстанавливается инструкция, выполненная с ошибкой, она повторяется сначала или с заранее определенной контрольной точки.

При успешном повторении осуществляется переход к продолжению нормальной работы процессора. При неуспешном выполнении всех попыток повторения БВ выдает сигнал прерывания от схем контроля, который может вызвать попытку обойти сбой программными методами восстановления,

включенными в программу потребителей. При безуспешных попытках неисправность классифицируется как отказ.

Восстановление В случае возникновения производится отказа обслуживающим персоналом с помощью системы диагностирования. Время поиска сокращено возможностью входа в любую зону диагностических тестов. Ошибки обнаруживаются размещенными в контрольных точках схемами контроля, которые сами могут оказаться неисправными. Наложение БВ неисправностей схем контроля И на неисправности основного оборудования снижает эффективность контроля. Ошибка, вызванная одной неисправностью основного оборудования, обычно выполняется несколькими схемами контроля, т. е. происходит распространение сигнала об ошибке. Однако существуют узлы в ЭВМ, пропадание сигнала ошибки в которых может привести к следующим последствиям:

данная ошибка не будет обнаружена вообще;

нарушатся условия повторения по сбою (в частности, адрес инструкции в дополнительном регистре хранения может содержать ошибку);

будет неверно определена область неисправности;

будет неверно определен тип неисправности (сбой может быть классифицирован как отказ).

Ясно, что такие узлы являются контрольными точками и в них обязательно должны быть размещены схемы контроля. Назовем контрольные точки, которые критичны к пропаданию сигнала ошибки, особыми. Для определения особых контрольных точек необходимо для каждой из них провести анализ на критичность пропадания сигнала ошибки. При этом следует учесть, что заведомо особыми являются такие контрольные точки, которые расположены в местах перехода от одного метода контроля к другому. Например, особыми являются точки перехода от контроля по четности к контролю дублированием и опять к контролю по четности в сумматорах.

Особыми являются схемы контроля дешифраторов и узлов, информация которых сохраняется для повторения. Очевидно, что БВ может быть рассмотрен как особая контрольная точка.

Таким образом, схемы контроля должны обнаруживать также сбои основного оборудования, интенсивность отказов которых на порядок выше интенсивности отказов, по которой определяется время T, не обнаруживаемые отказы и систематические сбои схем контроля особых контрольных точек могут привести к потере сигнала ошибки основного оборудования.

При ошибке единичные сигналы могут поступить на несколько входов БВ.

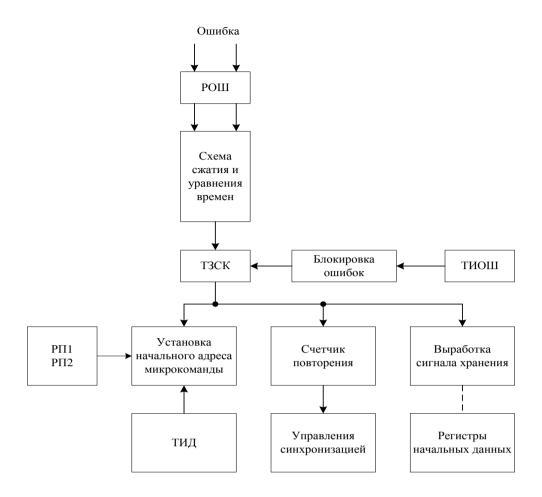

Блок восстановления рассматриваемого ЦП содержит регистр ошибок (РОш), схемы обработки ошибок и организации повторения, схемы управления синхроимпульсами и при использовании микросхем средней интеграции состоит из 8—10 ТЭЗ.

Последовательность обработки сигнала ошибки в БВ показана на рис.

1.2.3. Сигналы ошибок основного оборудования поступают на первый ряд триггеров РОш, содержимое которых обновляется в каждом машинном такте. Регистр ошибок разделен на группы по времени поступления сигналов ошибок. Прием ошибок в группе производится одним и тем же синхросигналом. Регистр занимает 100 логических элементов для 80 разрядов.

Схема сжатия и уравнивания времен содержит собирательные схемы и ряд триггеров, осуществляющих задержку сигналов ошибок.

Рис. 1.2.3. Последовательность обработки сигналов ошибки в блоке восстановления

На выходе первого ряда РОш сигналы ошибок объединяются по времени их возникновения. Уравнивание времен позволяет при блокировке синхросигналов иметь адрес микрокоманды, при выполнении которого возникла ошибка.

При отсутствии блокировки сигнал ошибки устанавливает триггер захвата от схем контроля (ТЗСК), что обеспечивает переход к микропрограмме обработки ошибок. Триггер игнорирования ошибок (ТИОш) блокирует установку ТЗСК от ошибок данных, поступающих при выполнении микропрограммы обработки ошибок. Схемы ТЗСК, ТИОш и блокировки занимают 15 логических элементов.

Единичное состояние ТЗСК блокирует сигнал «хранение», которым разрешается обновление начальных данных повторения, производимого на

основании анализа содержимого регистров повторения  $P\Pi_1$  и  $P\Pi_2$ , занимающих 30 логических элементов. Триггер исходных данных (ТИД) занимает 3 логических элемента, его состояние изменяется при изменении исходных данных команды.

#### 1.2.3. Построение отказоустойчивого ядра ТККС

Проведенный аналитический обзор построения отказоустойчивых функциональных узлов ЭВМ показывает что, при обеспечении отказоустойчивости данных систем необходимо использовать следующие принципы:

обеспечение отказоустойчивости к ошибкам типа "сбой" достигается повторением операции, возвратом к контрольной точке и программным рестартом;

обеспечение отказоустойчивости к константным ошибкам типа "const0 или const1" достигается на основе использования корректирующих кодов и структурных методов резервирования;

*Модульность*. Специализированная ЭВМ разбивается на отдельные функциональные блоки "модули" Для каждого модуля выбирается наиболее эффективный метод обеспечения отказоустойчивости;

*Быстрое проявление неисправности*. При возникновении ошибки модуль должен либо работать правильно (ошибка сразу корректируется), либо немедленно останавливаться (для предотвращения распространения ошибки).

*Независимость отказов.* Модули и связи между ними должны быть разработаны так, что отказ одного из модулей никак не влияет на работу остальных.

*Избыточность*. В систему должны быть заранее установлены или сконфигурированы запасные модули, так что при отказе одного из модулей, запасной модуль может заменить его практически немедленно. Отказавший

модуль может ремонтироваться автономно, в то время как система продолжает работать.

Для систем, у которых недопустимо даже кратковременное прерывание вычислительного процесса, требуется многократное резервирование.

Принципиальными требованиями к методам обеспечения отказоустойчивости систем, работающих в реальном масштабе времени, являются:

- высокая обнаруживающая способность (обнаруживать максимальное количество ошибок различной кратности);

- минимальное время обнаружения отказа;

- минимальные аппаратурные затраты на средства контроля;

- возможность обнаружения и определения места возникновения отказа;

- обнаружение и по возможности исправление ошибок, вызванных отказами;

- возможность замены неисправных блоков в процессе выполнения системой основных функций;

- отказоустойчивость системы не должна быть заметной для программиста пользователя.

В связи с тем, что ТККС, как правило, работают в реальном масштабе времени, для них могут быть использованы следующие методы обеспечения отказоустойчивости [42]:

методы простого резервирования;

методы избыточной логики с перекрестными соединениями;

мажоритарные методы резервирования;

методы, использующие корректирующие коды.

Из всех известных методов повышения достоверности функционирования в настоящее время широко применяется метод контроля по модулю, использующий контрольные символы, являющиеся остатками от деления чисел на некоторый модуль.

Однако определение контрольного остатка требует больших аппаратурных затрат и приводит к заметной потере быстродействия аппаратуры [9].

В связи с этим наиболее широко используется метод контроля на чётность (контроль по mod 2), требующий при реализации один контрольный разряд и минимальные аппаратурные затраты.

Недостатком метода контроля на четность является низкая обнаруживающая способность.

Существенным недостатком данного метода обнаружения ошибок является то, что он не обеспечивает отказоустойчивость рассматриваемой аппаратуры.

Недостатками метода поэлементного резервирования являются [12]:

- резкое увеличение резервного оборудования;

- увеличение нагрузки на отдельные компоненты, что приводит к снижению нагрузочной способности схем;

- повышение требований к допускам составляющих элементов, поскольку при выходе из строя некоторых элементов выходной сигнал должен оставаться в необходимых допусках.

Методы простого резервирования применительно к схемам, выполненным с высокой степенью интеграции, нецелесообразно использовать ещё и потому, что существенно возрастает число дополнительных связей, что приводит к снижению общей надёжности и существенно усложняет регулировку схем [73].

Избыточная логика с перекрёстными соединениями усложняет построение дискретных устройств, затрудняет их регулировку и диагностирование. Высокая надёжность достигается высокой ценой так, исправление одиночной ошибки требует увеличения аппаратуры в четыре раза [1].

В настоящее время наиболее часто используется мажоритарный метод резервирования. Достоинством метода является большая универсальность,

позволяющая использовать его на различных уровнях разделения дискретных устройств от отдельных узлов до резервирования устройства в целом.

Наиболее эффективным способом повышения отказоустойчивости и достоверности функционирования дискретных устройств является использование корректирующих кодов, позволяющих обеспечить аналогичный эффект при увеличении количества оборудования на 10...30% [9,42,58,63].

#### 1.3. Анализ резервирования на основе линейных кодов

## 1.3.1. Обоснование требований к методам кодирования информации функционального ядра ТККС

Появление корректирующих кодов связано с созданием помехоустойчивых каналов связи.

В основу построения корректирующих кодов для каналов связи положены следующие допущения [47,48]:

- надежность кодирующих и декодирующих устройств предполагается несравнимо более высокой, чем надежность каналов связи, поэтому проблемы, "кто будет сторожить сторожа", для каналов связи не существует, а сложность кодирующих и декодирующих устройств не является определяющим параметром;

- ошибки в каналах связи взаимонезависимы (даже в случае пакета ошибок, внутри пакета ошибки предполагаются независимыми) и, как следствие, вероятность появления ошибок с увеличением их кратности резко падает.

Основным критерием эффективности применения корректирующих кодов в каналах связи является получение максимальной скорости передачи информации при заданной корректирующей способности кода. Это означает, что скорость тем выше, чем больше отношение k/n (где k — число информационных символов кода, n - общая длина кода) при заданной

кратности d исправляемых ошибок. Поэтому наиболее эффективным с указанной точки зрения являются плотноупакованные коды (совершенные коды). К таким кодам относятся коды Хемминга, коды Голея и код с повторением.

При использовании корректирующих кодов в вычислительных каналах к ним предъявляются требования, отличные от требований, предъявляемых к кодам для каналов связи.

Прежде всего, надежность кодирующих и декодирующих устройств соизмерима с надежностью самого вычислительного канала. Отсюда вытекает необходимость повышения надежности данных устройств. Это можно осуществить, во-первых, применением низкоплотных кодов, проверочные (порождающие) матрицы которых содержат существенно меньшее число единиц по сравнению с плотноупакованными кодами, что упрощает реализацию кодирующих и декодирующих устройств, во-вторых, организацией защиты последних от собственных ошибок.

Критерием эффективности применения корректирующих кодов в вычислительных каналах служит не максимизация отношения k/n, а получение максимума надежности вычислительного канала с коррекцией ошибок при минимуме аппаратурных затрат.

В вычислительных каналах, как правило, проводится параллельная обработка информации. Скорость обработки определяется как сумма задержек в самом канале и в кодирующем, и особенно в декодирующем устройствах. Поэтому корректирующие коды, используемые в вычислительном канале, и, прежде всего, в запоминающих устройствах (ЗУ), должны обеспечивать минимальную глубину кодирования и декодирования. Наиболее полно этому требованию удовлетворяют низкоплотные коды.

В вычислительном канале кратность ошибок во многом определяется структурой устройств, так как однократный отказ в результате имеющихся в схеме разветвлений может привести к многократной ошибке на выходе.

Этим, в частности, объясняется сравнительно слабое использование корректирующих кодов в цифровых устройствах с произвольной структурой. Кроме того, поскольку устройства обработки и хранения информации реализуются на интегральных микросхемах (ИМС), в том числе БИС, имеющих от единиц до нескольких десятков выводов, нельзя утверждать, что ошибки на отдельных выводах одной ИМС взаимонезависимы. Дефект в кристалле или подложке ИМС может привести к появлению пачки ошибок на ее выходах. Очевидно, что при формировании кодовых слов пачки ошибок на выходах отдельных ИМС будут занимать строго определенное положение. Такие фиксированные (фазированные) пачки ошибок получили название байтов ошибок. Этот класс ошибок свойственен только вычислительному каналу (не следует смешивать понятие байта ошибок, размерность которого произвольна, и байта информации, под которым в вычислительной технике понимается восьмиразрядное двоичное слово).

В целях повышения достоверности работы цифровых устройств и улучшения их эксплуатационных характеристик целесообразно наряду с исправлением ошибок осуществлять и обнаружение ошибок. Корректирующий код (линейный или нелинейный) с минимальным кодовым расстоянием  $D_0$  исправляет ошибки кратности  $d \leq [(D_0-1)/2]$  или обнаруживает ошибки кратности  $d \leq D_0-1$  (знак [47] означает округление до ближайшего меньшего целого числа).

Для того чтобы с помощью кода можно было одновременно исправлять ошибки кратности  $d_1$  (и менее) и обнаруживать ошибки кратности d (и менее), причем  $d_1 > d$ , необходимо выполнять условие  $D_0 \ge d + d_1 + 1$ . В этом случае сигнал ошибки кратности d означает, что ошибка была, но исправлена, и дефект должен быть устранен в период проведения ремонта устройства. Сигнал ошибки кратности  $d_1$  показывает, что с декодирующего устройства снимается неправильная информация, при этом сигнал ошибки может быть использован для блокирования этой информации.

Таким образом, корректирующие коды, предназначенные для устройств обработки и хранения информации, должны:

иметь кодирующие и декодирующие устройства минимальной сложности; иметь декодирующие устройства, защищенные от собственных отказов;

иметь минимальные задержки в кодирующем и декодирующем устройствах (минимальную глубину кодирования и декодирования), что требует реализации параллельного способа декодирования;

обеспечивать как коррекции случайных независимых ошибок кратности d, так и коррекцию байтов ошибок длины b (b>d);

позволять осуществлять раздельное обнаружение ошибок кратности d и d+1 (b и b+1).

Исходя из перечисленных требований в вычислительных каналах могут быть использованы блоковые линейные и нелинейные коды. Применение циклических кодов нецелесообразно, так как они реализуют последовательный метод декодирования, требующий существенно большего времени, чем метод параллельного декодирования.

## 1.3.2. Выбор метода кодирования, обеспечивающего минимальную сложность декодирующего устройства

Линейные коды допускают три метода параллельного декодирования: декодирование методом дизъюнктивных сфер;

синдромное декодирование;

мажоритарное декодирование.

Первый метод декодирования требует существенно больших аппаратурных затрат, по сравнению с двумя другими, и поэтому его использование является нецелесообразным [42].

Декодирование, использующее стандартное расположение, является декодированием по методу максимума правдоподобия.

В этом случае предполагается, что кратность ошибки не превышает корректирующую способность выбранного кода.

На практике данное ограничение является не всегда оправданным, так как под воздействием внешних воздействий, влияющих одновременно на все

элементы дискретного устройства, возможно возникновение ошибки, превышающей кратность корректируемой. Однако в данном случае лидер смежного класса будет выбран неправильно, что приведет к неправильной коррекции ошибки.

В связи с этим при построении отказоустойчивых устройств необходимо использовать корректирующие коды, исправляющие ошибки заданной кратности при условии обнаружения максимального количества некорректируемых ошибок.

Достоверность функционирования отказоустойчивого дискретного устройства во многом определяется аппаратурными затратами (надежностью) декодирующих устройств обнаружения и коррекции ошибок.

Таким образом, для построения отказоустойчивых дискретных устройств необходимо использовать корректирующие коды:

с минимальной сложностью декодирующего устройства;

повышенной корректирующей способности ( $v = 1 \div k$ );

повышенной обнаруживающей способности (обнаруживать некорректируемые ошибки).

Необходимость использования корректирующих кодов, требующих минимальных аппаратурных затрат на построение декодирующего устройства, заставляет искать специальные классы кодов, для которых существует простой метод декодирования. К таким кодам относят низкоплотные коды [9].

Наименьшую сложность декодирующего устройства (  $P_{\text{ДЕК}} o \max$  ) и минимальную глубину декодирования (  $t_{\min}$  ) имеют низкоплотные линейные коды, у которых k=r .

Низкоплотные коды описываются матрицей, содержащей преимущественно нули и сравнительно небольшое количество единиц, тем самым уменьшается количество символов, входящих в контрольные соотношения. При увеличении r (уменьшении j) увеличивается число

контрольных соотношений, что приводит к увеличению аппаратурных затрат на декодирование. Минимальное количество символов, входящих в контрольные соотношения низкоплотных кодов, позволяют обеспечить минимальные временные затраты на декодирование, так как на пути прохождения сигнала находится минимальное количество сумматоров по mod2.

### 1.3.3. Исследование коррекции ошибок заданной кратности

При обосновании кратности корректируемых и обнаруживаемых ошибок необходимо учитывать особенности конструктивного исполнения функциональных узлов вычислителя.

В связи с тем, что многие дискретные узлы вычислителей реализуются на отдельных интегральных микросхемах, имеющих от единицы до нескольких десятков выходов, нельзя утверждать, что ошибки на отдельных выводах ИМС взаимно независимы. Отказ в кристалле или подложке ИМС может провести к пачке ошибок (ошибкам модульного типа на её выходах). Поэтому при резервировании дискретных узлов особую актуальность приобретает задача коррекции ошибок заданной кратности и ошибок модульного типа.

Обычно в качестве кодов, исправляющих любые две и обнаруживающих любые три ошибки, применяются коды Боуза-Чаудхури-Хоквингема (БЧХ–коды) с расстоянием d=6 [71]. Порождающим многочленом такого кода является многочлен  $g(x)=(x+1)p_1(x)p_3(x)$ , где неприводимый многочлен  $p_3(x)$  имеет своим корнем элемент  $a^3$ . Длина кода является наименьшим общим кратным порядка элементов а и  $a^3$  в мультипликативной группе поля  $GF(2^m)$ . И если хотя бы один из многочленов  $p_1(x)$  и  $p_3(x)$  примитивный, то длина кода  $n=2^m-1$ ,однако чаще всего она связана с различными техническими ограничениями, в силу которых число информационных символов равно

степени двойки. Поэтому на практике применяются укороченные коды БЧХ [50].

Частным видом кодов БЧХ являются коды Рида-Соломона, используемые для исправления ошибок модульного типа.

Однако использование данных кодов для резервирования дискретных устройств, работающих в реальном масштабе времени, практически неприемлемо из-за больших аппаратурных затрат на кодирование и декодирование и большой глубины декодирования (низкое быстродействие, так как реализуется процедура декодирования циклических кодов).

Заметим, что коды РС допускают мажоритарный метод декодирования, но, как отмечается в [5,71,50] практически это неприемлемо.

Большой практический интерес для коррекции ошибок байтового типа представляют коды с коррекцией ошибок в одной группе бит и обнаружения ошибок в двух группах, являющихся модификацией кода Хемминга [65].

Недостатком данных кодов является сложность (аппаратурные затраты) алгоритма декодирования и, следовательно, низкая надёжность (достоверность функционирования) резервированного устройства.

# 1.3.4. Проблема использования корректирующих кодов для обеспечения отказоустойчивости функционального ядра

Контроль арифметических операций функционального ядра системы управления

Все рассмотренные выше коды использовались для контроля передачи информации. Особенностью подобного вида контроля является то, что с его помощью решается сравнительно несложная задача — убедиться в неизменности передаваемой информационной комбинации или восстановить эту информацию, если в ней произошли искажения. Совсем другие требования возникают при контроле обрабатываемой информации, которая не остается постоянной, а все время изменяется в процессе тех или иных

операций. Следовательно, в этом случае необходимо обеспечить контроль правильности ее преобразования, т.е. правильности выполнения этих операций. И если возникшая ошибка при передаче информации искажает одно число или отдельные числа, не связанные друг с другом, то та же ошибка при расчетах начинает распространяться в вычислительном процессе, поскольку исходные данные одной операции являются результатом предшествующих операций.

Из множества разработанных методов контроля арифметических операций наибольшее распространение получил контроль по модулю, который называют также контролем по остаткам или наименьшим вычетам. Суть организации такого контроля заключается в том, что каждому числу, участвующему в операции, ставится в соответствие контрольный код, который представляет собой остаток от деления контролируемого числа на некоторое заранее заданное целое число q, называемое модулем. Использование остатка в качестве контрольного кода возможно по той причине, что любое число A сравнимо с этим остатком.

При выполнении операции над числами та же операция выполняется над их контрольными кодами, после чего контрольный код результата основной операции сравнивается с результатом аналогичной операции над контрольными кодами исходных чисел.

Для нахождения остатка от деления двоичного числа на модуль 3 достаточно просуммировать цифры разрядов контролируемого числа по модулю 3 с учетом знаков четных и нечетных разрядов, что удовлетворяет второму условию.

Одиночная ошибка в одном из разрядов двоичного числа соответствует его изменению на  $\pm 2^i$ . Для возможности обнаружения ошибки необходимо, чтобы контрольные коды чисел A и  $A\pm 2^i$  не совпадали, т.е. нужно выполнить условие

$$R(A) \neq R(A \pm 2^i)$$

Поскольку  $2^i$  не делится на три без остатка, последнее условие всегда выполняется. Кроме одиночных ошибок, контроль по модулю 3 выявляет все двойные ошибки, для которых справедливо указанное условие.

Контроль логических операций функционального ядра

Контроль логических операций, в частности таких поразрядных операций, как логическое сложение (ИЛИ), логическое умножение (И) и исключающее ИЛИ (сложение по модулю 2 или операция неравнозначности), не имеет такой структуры, как контроль арифметических операций. Объясняется это тем, что в отличие от арифметических логические операции выполняются поразрядно и результат операции в каждом конкретном разряде определяется только состоянием соответствующих разрядов операндов, не связанных с другими разрядами чисел. Следовательно, для большинства логических операций невозможно найти общие контрольные разряды, которые оказались бы совместимыми с данной операцией. Реализация же поразрядного схемного контроля в принципе возможна, но неэкономична, так как это потребует резкого увеличения контрольной аппаратуры.